Last Updated: 2023-09-06 03:11:03 Wednesday

-- TOC --

学习Verilog,肯定需要一款编译仿真软件。经过一番折腾,我发现有免费正版的ModelSim可以用,还有开源的Verilator等。

ModelSim是Mentor Graphics公司开发的优秀的HDL语言仿真软件,可以做Verilog代码仿真。它提供还算友好方便的仿真环境,采用单内核支持VHDL和Verilog混合仿真的仿真器。它采用直接优化的编译技术、Tcl/Tk技术和单一内核仿真技术,编译仿真速度快且编译的代码与平台无关。它可以在Windows系统下运行。

一句话:ModelSim软件可以用来仿真Verilog代码。

2017年3月,西门子以45亿美元收购Mentor Graphics,并入西门子数字化工业软件部门(Digital Industry Software),自此以后Mentor对外的名称一直是“Mentor, a Siemens Business”。

显然,这是一款收费软件。(开头说是免费的呢?别急,往下看...)

官方网站:https://eda.sw.siemens.com/en-US/ic/modelsim/

ModelSim有几种不同的版本:SE、PE、LE和OEM,其中SE是最高级的版本,而集成在 Actel、Atmel、Altera、Xilinx以及Lattice等FPGA厂商设计工具中的均是其OEM版本。

OEM版本,有免费的,不需要License。

Intel收购了Altera,它的FPGA开发套件Lite版本(或Starter版本),就含有ModelSim,在安装的时候,可以选择不需要License安装。我觉得对于学习Verilog来说,肯定够用了。

地址:https://fpgasoftware.intel.com/?edition=lite

成功下载的代价,就是你需要在Intel网站上注册一个账号。

Lattice也是一家FPGA供应商,纳斯达克上市,不过它的市场份额比较小,我看资料上说大概在4%左右。它提供的开发软件Lattice Diamond,也含有ModelSim,也可以免费使用。

地址:https://www.latticesemi.com/Products/DesignSoftwareAndIP/FPGAandLDS/LatticeDiamond

代价同样是需要在他家的网站上注册一个账号,然后去申请一个免费的License,都能够申请到,一个License管一年,到期后再申请。

以上就是获取正版免费ModelSim的方法。

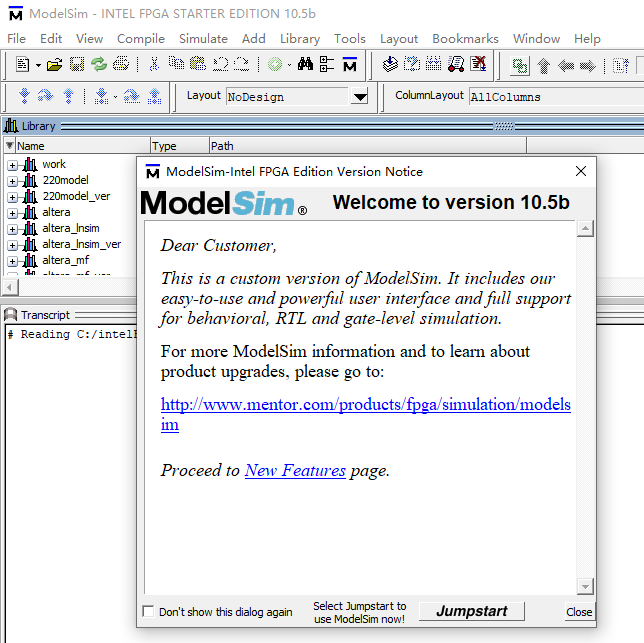

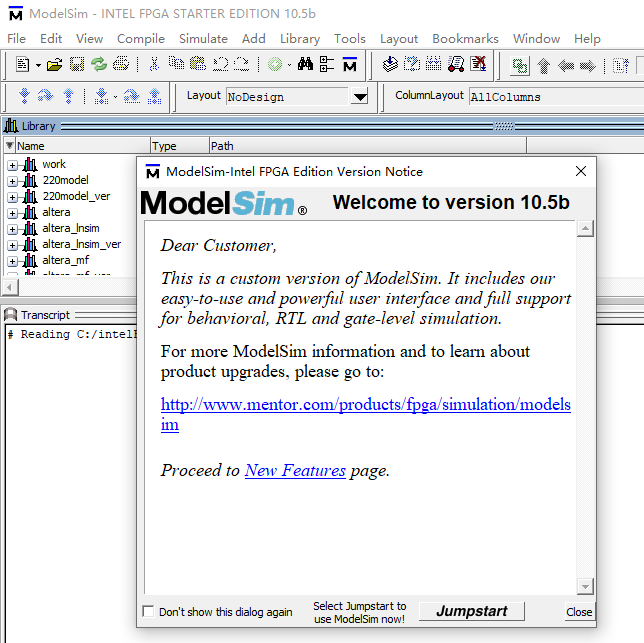

我选择了Intel,新手入门,反正都要注册账号,Intel的ModelSim不需要额外申请License。这个版本是10.5b的:

网络上有很多人使用ModelSim的破解版,因为免费得到的版本功能受限,可能主要是仿真速度慢吧,我还没有这方面经验。

SE版和OEM版在功能和性能方面有较大差别,比如对于大家都关心的仿真速度问题,以Xilinx公司提供的OEM版本ModelSim XE为例,对于代码少于40000行的设计,ModelSim SE比ModelSim XE要快10倍。对于代码超过40000行的设计,ModelSim SE要比ModelSim XE快近40倍。

有兴趣的同学,可以看看这个地址:https://blog.csdn.net/QWERTYzxw/article/details/115350715

不想用ModelSim破解版,又嫌弃免费版的速度,可以考虑开源的Verilator。它是一个LinuxFoundation支持的开源项目,可以将Verilog代码翻译成C++代码,然后编译执行仿真。

Verilator官网:Verilator

Linux平台下,优先考虑使用Verilator。看波形图,要配合GTKwave。具体细节就不再这篇文章里面介绍了。

一个良心网站,既可以学习Verilog,还可以在线做仿真。

地址:https://hdlbits.01xz.net

网站作者是一个计算机博士,也是高校的老师,他说他发现学生们初学Verilog时,学习曲线是很陡峭的,因为有大量的新知识,还有很多软件要准备,特别是仿真软件。而学习Verilog最重要的就是practice,于是他就搞了这个网站,既可以学习,还可以在线做仿真,how nice...:)这个作业还有几个其它学习网站都非常nice。

有了Verilog编译仿真软件,就可以正式开始Verilog硬件设计之路!Good Luck!练习练习再练习...我会尽可能将学习过程中所总结的知识和代码共享在这个网站上。

本文链接:https://cs.pynote.net/hd/verilog/202109151/

-- EOF --

-- MORE --